# POWER EFFICIENT FREQUENCY DIVIDER CIRCUIT BASED ON ADAPTIVE VOLTAGE LEVEL TECHNIQUE

<sup>1</sup>Vivek Saxena, <sup>2</sup>S.R.P Sinha, <sup>3</sup>Subodh Wairya

<sup>1</sup>M.Tech Scholar, <sup>2</sup>Professor, <sup>3</sup>Professor,

<sup>1</sup>Electronics Department,

Institute of Engineering and Technology, Lucknow, India.

**Abstract:** In the recent trends, power optimisation has become an important factor in integrated circuits. In this paper, a frequency divider circuit has been proposed which consumes less power based on adaptive voltage level at supply (AVLS) technique. In this technique, the supply voltage potential is reduced so as to reduce the power consumption of certain transistors. The aim of this paper is to investigate the power dissipation of the proposed design. The circuit is designed using DSCH and Microwind softwares using 90 nanometer and 45 nanometer technology respectively.

IndexTerms - Frequency Divider, CMOS, 45 nanometer technology, Adaptive voltage level, AVLS.

## I. INTRODUCTION

The recent trend of compact devices in the field of electronics has led to the requirement of circuits that consume lower power as compared to their conventional counterparts. The main motivation for this low power design is the prolonged battery life and reliability.

This motivation has led to the discovery of technologies in digital systems such as NORA [2] and DOMINO [1] logic based technologies. The advantage with these technologies was that they consumed lesser power as compared to their conventional counterparts but they possessed the problem of charge sharing. This charge sharing problem can be addressed by using a single phase clocking. This led to the development of TSPC [3] logic circuits and AVL [4] design style. All the above mentioned techniques aim at reducing the dynamic power consumption.

In the field of digital circuits, sequential circuit is a circuit whose output at any state depends on the present input as well as the past state outputs. The simplest type of sequential circuit is a memory element cell which has two states. The states can either be 1 or 0. These kind of sequential circuits are called flip flops, since they flip from one state to another and then flip back to the previous state.

One of the simplest flip flops is the set reset flip flop. The disadvantage of this flip flop is that the output cannot be determined if both the inputs S and R are equal to 1 simultaneously. In order to eliminate this problem, another flip flop in which an inverter is used in addition to the input is made. This flip flop is known as a D flip flop and in this flip flop the output follows the input.

One of the key applications of the D flip flop is the frequency divider circuit, which takes the input as a frequency and produces the output whose frequency is divided by a factor of two.

The frequency divider circuits were conventionally made mainly by using either source coupled logic (SCL) [4] or injection locked topology [5]. The problem with these kind of designs was that when the devices were operated at the voltages below 1 volt, the performance of these devices degraded significantly and some of them even failed to function. The improvement over these design style were NORA and DOMINO design logic styles but they suffered from the problem of charge sharing. When the frequency divider circuit is made by using TSPC design style, it consumes lesser power and the problem of charge sharing which was apparent in NORA and DOMINO logic is reduced further.

### II. PROPOSED FREQUENCY DIVIDER CIRCUIT

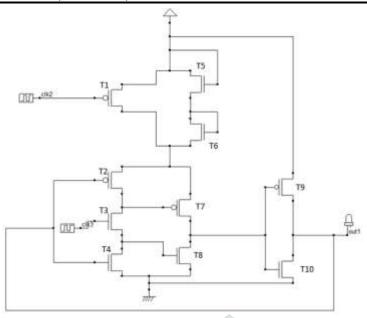

In the proposed frequency divider, we are going to use an AVLS based D flip flop which is inherently based upon TSPC design style. For the designing of this frequency divider circuit we are going to provide the output of the circuit in feedback to the input of the circuit. The AVLS circuitry applied at the supply side is going to reduce the supply voltage and this reduction in supply voltage subsequently results in lesser power consumption of the transistors. The purpose of clk2 and the control circuit which consists of transistors T1, T5 and T6 is to reduce the leakage power consumption.

Figure 1: Schematic representation of frequency divider circuit using AVLS technique.

#### III. SIMULATION AND RESULTS

The simulation is done on MICROWIND 3.5 and its DSCH tool.

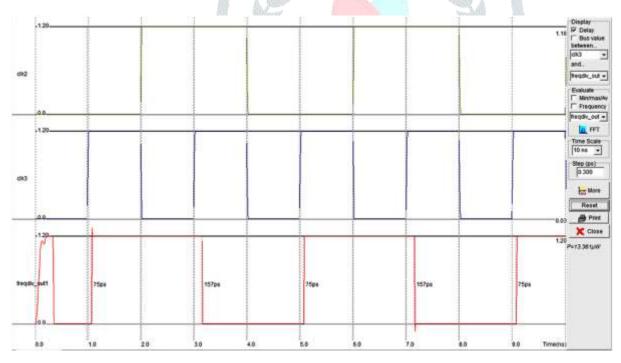

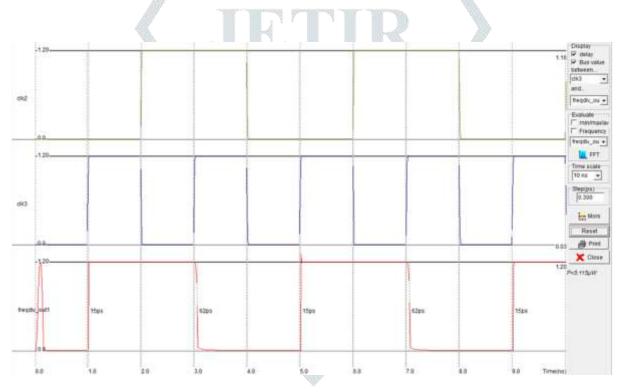

The simulation shows the relation between the input frequency clk3 and output frequency frediv\_out1. The output frequency is divided by a factor of 2.

Figure 2: Waveform and Power consumption of the proposed circuit using 90 nm technology.

© 2020 JETIR September 2020, Volume 7, Issue 9

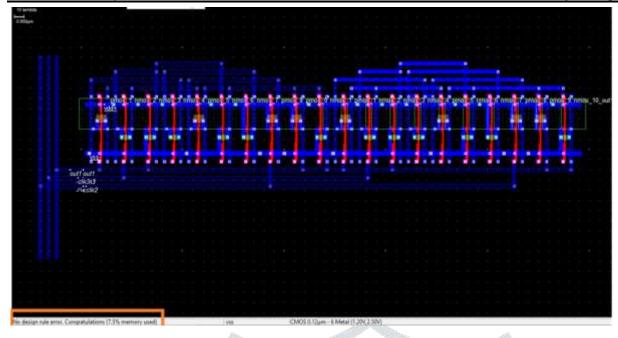

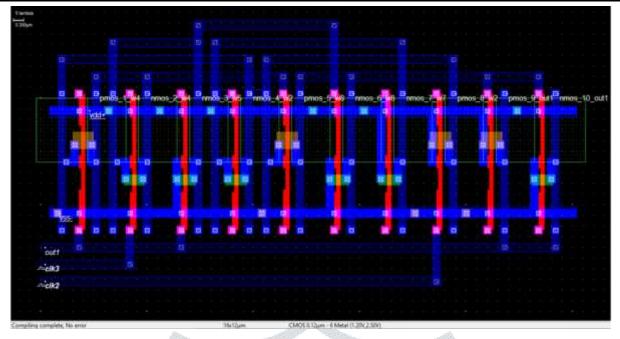

Figure 3: Layout design of the proposed circuit using 90 nm technology. The orange box shows there is no design rule error.

Figure 4: Waveform and Power consumption of the proposed circuit using 45 nm technology.

Figure 5: Layout of the proposed circuit using 45nm technology.

#### IV. RESULTS AND DISCUSSION

We have been able to achieve a power reduction of 99.5% power reduction when the circuit is implemented by using 45 nanometer technology compared to a contemporary design by Kailuke[9] and the reduction in layout area is 74.61%. The circuit is able to process maximum frequency of 12.5 Giga Hertz, which is good when compared to other frequency divider circuits. The only drawback is the lowest frequency of operation which is 200 Mega Hertz. The circuit by Kailuke [9] was able to process frequencies as low as 2 Mega Hertz. This makes the proposed circuit suitable for low power applications.

| Table 1: Comparison of parameters of Co | ontemporary Frequency | y Divider circuits with the prop | osed circuits. |

|-----------------------------------------|-----------------------|----------------------------------|----------------|

|                                         |                       |                                  |                |

| ·           |                     | W alle               |               |                    |

|-------------|---------------------|----------------------|---------------|--------------------|

| PARAMETER   | RAZAVI[7]           | KAILUKE[9]           | PROPOSED      | PROPOSED           |

|             |                     |                      | CIRCUIT       | CIRCUIT            |

|             |                     |                      | USING 90nm    | USING 45nm         |

| TECHNOLOGY  | 0.1µm               | 0.18µm               | 90nm          | 45nm               |

| POWER       | 2.6mW               | 1mW                  | 13.36µW       | 5.115µW            |

| CONSUMPTION |                     |                      |               |                    |

| MINIMUM     | 5GHz                | 2MHz                 | 200MHz        | 200MHz             |

| OPERATING   |                     |                      |               |                    |

| FREQUENCY   |                     |                      |               |                    |

| MAXIMUM     | 13.6GHz             | 2.3GHz               | 12.5GHz       | 12.5GHz            |

| OPERATING   |                     |                      |               |                    |

| FREQUENCY   |                     |                      |               |                    |

| NUMBER OF   | 12                  | 12                   | 10            | 10                 |

| TRANSISTORS |                     |                      |               |                    |

| LAYOUT AREA | 3500µm <sup>2</sup> | 756.3µm <sup>2</sup> | $384 \mu m^2$ | 192µm <sup>2</sup> |

#### REFERENCES

- R. H. Krambeck, C. M. Lee, and H. S. Law, "High-speed compact circuits with CMOS," IEEE J. Solid-State Circuits, vol. 17, pp.,614–619, June 1982.

- [2] N. P. Goncalves and H. J. de Man, "NORA: Aracefree dynamic CMOS technique for pipelined logic structures," IEEE J. Solid-StateCircuits, vol. 18, pp. 261–268, June 1983.

<sup>[3]</sup> J. Yuan and C. Svensson, "High-speedCMOS circuit technique," IEEE J. Solid-StateCircuits, vol. 24, pp. 62–70, Feb. 1989.JETIR2009179Journal of Emerging Technologies and Innovative Research (JETIR) www.jetir.org1307

#### © 2020 JETIR September 2020, Volume 7, Issue 9

- [4] R. Chen, "High-speed CMOS frequency divider," Electron. Lett., vol.33, no. 22, pp. 1864–1865, Oct. 1997.

- [5] H. Wang, "A 1.8-V 3-mW 16.8-GHz frequency divider in 0.25 micrometerCMOS," in IEEE Int. Solid-State Circuits Conf. Dig. Tech. Papers, Feb.2000, pp. 196–197.

- [6] R. J. Bakcer, H. W. Li and D. E. Boyce, "CMOS design, layout and simulation", IEEE Press, 1998.

- [7] Behzad Razavi, Kwing F. Lee And Ran H. Yan, "Design Of High Speed, Low Power Frequency Dividers And Phase-Locked Loops In Deep Submicron Cmos", IEEE Journal Of Solid State Circuits, Vol 30, No 2, February 1995

- [8] Joseph M.C. Wong, Vincet S. L. Cheung And Howard C. Luong, "A 1-V 2.5-Mw 5.2 Ghz Frequency Divider In A 0.35 Micrometer Cmos Process", IEEE Journal Of Solid State Circuits, Vol 38, No 10, October 2003

- [9] Aniruddha C. Kailuke, Pankaj Agarwal And R.V. Kshirsagar, "Design Of High Speed, Low Power Frequency Dividers For High Speed Frequency Synthesiser In 0.18 Micrometer Cmos Process", Indian Journal Of Applied Research, Vol 6, Issue 4, April 2016

- [10] Y. Suzuki, K Odagawa, And T Abe, " Clocked Cmos Calculator Circuitry," IEEE Journal on Solid-State Circuits, Vol. 8, Pp. 462–469, Dec. 1973.

- [11]. R. H. Krambeck, C. M. Lee, And H. S. Law, "High-Speed Compact Circuits With Cmos," IEEE J. Solid-State Circuits, Vol. 17, Pp.614–619, June 1982.

- [12] H. Oguey And E. Vittoz, "CODYMOS Frequency dividers Achieve Low Power Consumption and High Frequency," Electron.Lett., Vol. 9, Pp.386–387, Aug. 1973

- [13] H. Wang, "A 1.8-V 3-Mw 16.8-Ghz Frequency Divider In 0.25 Micrometer CMOS," In IEEE Int. Solid-State Circuits Conf. Dig. Tech. Papers, Feb.2000, Pp. 196–197.

- [14] T. Fuse Et Al., "A 1.1-V SOI CMOS Frequency Divider Using Body-Inputting SCL Circuit Technology," In IEEE International SOI Conference, Oct. 2000, Pp.106–107.